Product Summary

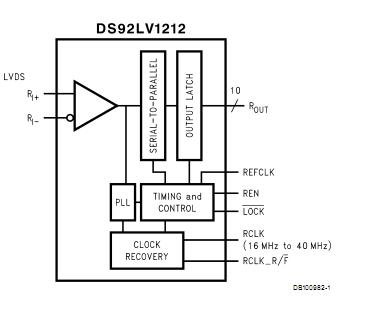

The DS92LV1212TMSA is a 10-Bit Bus LVDS Random Lock Deserializer. It maintains all of the features of the DS92LV1210 with the additional capability of locking to the incoming data stream without the need of SYNC patterns. The DS92LV1212TMSA receives a Bus LVDS serial data stream and transforms it into a 10-bit wide parallel data bus and separate clock. The DS92LV1212TMSA will establish lock to a synchronization pattern within specified lock times but it can also lock to a data stream without SYNC patterns.

Parametrics

DS92LV1212TMSA absolute maximum ratings: (1)Supply Voltage (VCC):-0.3V to +4V; (2)CMOS/TTL Input Voltage:-0.3V to (VCC +0.3V); (3)CMOS/TTL Output Voltage:-0.3V to (VCC +0.3V); (4)Bus LVDS Receiver Input Voltage:-0.3V to +3.9V; (5)Junction Temperature:+150℃; (6)Storage Temperature:-65℃ to +150℃; (7)Lead Temperature(Soldering, 4 seconds):+260℃.

Features

DS92LV1212TMSA features: (1)Clock recovery without SYNC patterns-random lock; (2)Guaranteed transition every data transfer cycle; (3)Chipset (Tx + Rx) power consumption < 300mW (typ) @ 40MHz; (4)Single differential pair eliminates multi-channel skew; (5)400 Mbps serial Bus LVDS bandwidth (at 40 MHz clock); (6)10-bit parallel interface for 1 byte data plus 2 control bits or UTOPIA I Interface; (7)Synchronization mode and LOCK indicator; (8)Flow-through pinout for easy PCB layout; (9)High impedance on receiver inputs when power is off; (10)Programmable edge trigger on clock; (11)Footprint compatible with DS92LV1210; (12)Small 28-lead SSOP package-MSA.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

DS92LV1212TMSA |

|

IC DESERIALZR RANDOM LOCK 28SSOP |

Data Sheet |

|

|

||||||||||||

|

DS92LV1212TMSA/NOPB |

National Semiconductor (TI) |

LVDS Interface IC |

Data Sheet |

|

|

||||||||||||

|

DS92LV1212TMSAX |

|

IC DESERIALZR RANDOM LOCK 28SSOP |

Data Sheet |

Negotiable |

|

||||||||||||

(China (Mainland))

(China (Mainland))